# LOW OUTPUT CONDUCTANCE, HIGH CUTOFF FREQUENCY TRANSISTORS FOR GATE ARRAY IMPLEMENTATION OF ANALOG CIRCUITS

Itamar José Bassanezi Loss, Carlos Galup Montoro and Márcio Cherem Schneider

LINSE - EEL - UFSC Caixa Postal 476 88010-970 - Florianópolis - SC - Brazil e-mail: linse@brufsc.bitnet Fax: (0482) 319770

Fone: (0482) 319643 / 319504

### ABSTRACT

This paper presents a simple approach to design low output conductance composite transistors, wider at the drain end than at source end. These transistors have two main advantages over "DC equivalent" transistors of uniform width: significant silicon area savings and an increase in the cutoff frequency. The main envisaged application is the integration of analog circuits in digital gate arrays.

## I. INTRODUCTION

The MOS technology has proven to be well suited for the implementation of mixed analog-digital systems. To increase design speed the gate array approach has been extensively used for digital circuits. However, only very few gate array implementations of combined analog and digital circuits have been reported [1-3]. Gate array transistors usually have minimum channel lengths. Although this feature is desirable in digital applications, several transistor channel widths and lengths are needed for precision analog circuits. It has been pointed out [1] that parallel connection of unit transistors yields wide-channel transistors while serial connection produces long-channel transistors. However, the transit time of the series connected transistors is proportional to the square of the number of series transistors.

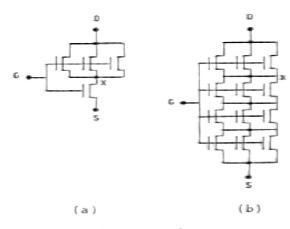

This paper presents a simple method to design composite MOS devices consisting of associations of unit transistors. It is shown that the T-transistor of Fig. 1 (a), with the drain end wider than the source end, has almost the same DC characteristics as the R-transistor of Fig. 1 (b). Two advantages are obtained from using a T-transistor in lieu of an R-transistor: area savings and an increase in the cutoff frequency.

## II. DC CHARACTERISTICS

In the triode region, using the gradual channel approximation, the drain current I<sub>d</sub> of an MOS transistor can be written [4] as

$$I_{d} = K[g(v_{g}, v_{d}) - g(v_{g}, v_{s})]$$

(1)

where all voltages are referred to the substrate voltage, emphasizing the symmetry between drain and source.

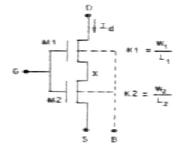

From eqn. (1), the following expression holds for the composite transistor shown in Fig. 2

$$g(v_{g}, v_{x}) = \frac{K1}{K1 + K2}g(v_{g}, v_{d}) + \frac{K2}{K1 + K2}g(v_{g}, v_{s})$$

(2)

Hence, the drain current in the composite transistor is:

$$I_{d} = \frac{K1.K2}{K1 + K2} [g(v_{g}, v_{d}) - g(v_{g}, v_{s})]$$

(3)

Therefore, in the triode region, the composite transistor has a DC behavior equal to that of a single transistor whose aspect ratio is K1 K2/(K1+K2). Moreover, two transistors are also equivalent in the saturation region if they have:

- (i) the same aspect ratio K

- (ii) the same channel width at the drain end.

Satisfied these conditions, it can be verified that the current density and the electrical field at the channel end near the drain are almost the same. Therefore, the composite transistors in Fig. 1 are equivalent at DC. Notice that the transistors connected between nodes X and S in Fig. 1 are always in the triode region provided the transistors connected to the drain end are not in punch-through.

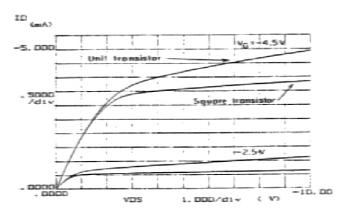

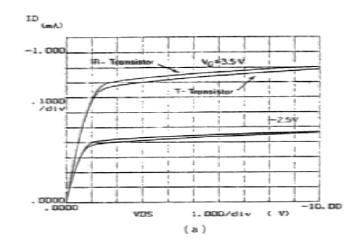

Fig. 3 shows the DC output characteristics of a unit transistor and of a square (3x3) composite transistor. Their equivalence in the triode region and the smaller output conductance of the composite transistor in saturation are readily verified.

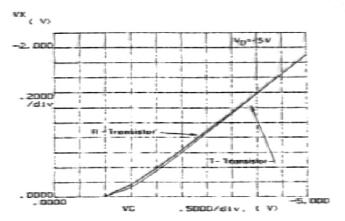

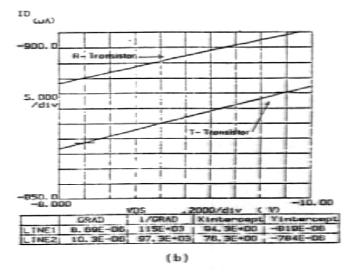

The DC equivalence of the composite transistors of Fig. 1 is illustrated in Figs. 4 and 5. In Fig. 4, the two plots of the internal potential  $V_X$  are almost coincident, in particular for high values of the gate voltage. Fig. 5 shows the DC output characteristics of the two transistors. These characteristics are also almost coincident, particularly the output conductance in the saturation region.

The transit time in an MOS transistor is given by [4]:

$$\tau = \frac{Q_1}{I_d} \tag{4}$$

where Q<sub>1</sub> is the total inversion charge.

The transit time of the saturated trapezoidal transistor (Fig. 1), calculated in strong inversion using the approximations for the inversion charge and the drain current presented in reference [5], is given by

$$\tau = \tau_{u} \left[ \sqrt{1 + m} \left( 1 - \frac{1}{m^{2}} \right) + \left( 1 + \frac{1}{m} \right)^{2} \right]$$

(5)

where  $\tau = \tau_u$  is the transit time of the unit transistor in saturation and m is the number of parallel-connected unit transistors at the drain side.

In order to evaluate experimentally expression (5), the normalized transit time can be written as:

$$\frac{\tau}{\tau_{u}} = \frac{C_{gs}}{C_{gsu}} \frac{g_{mu}}{g_{m}}$$

(6)

where C<sub>gs</sub> is the gate-to-source capacitance and g<sub>m</sub> is the small-signal gate transconductance [4].

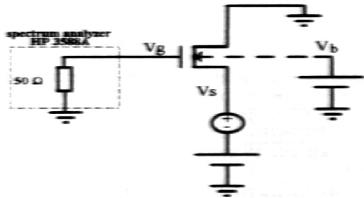

g<sub>m</sub> and g<sub>mu</sub> have been measured in an HP 4145B semiconductor parameter analyzer while C<sub>gs</sub> and C<sub>gsu</sub> have been measured according to the electrical scheme shown in Fig. 6.

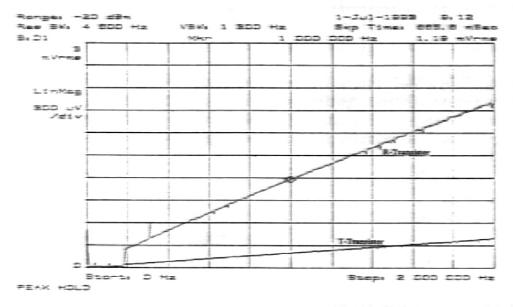

Fig. 7 shows the experimental results obtained from the circuit in Fig. 6 for both the T-transistor and the R-transistor from Fig. 1. The capacitive coupling in the R-transistor is about 6 times larger than in the T-transistor. Clearly, the transit time of the T-transistor is smaller than the transit time of the R-transistor due to a shorter distance between points S and X. Moreover, the gate area of the T-transistor is reduced, relative to the R-transistor.

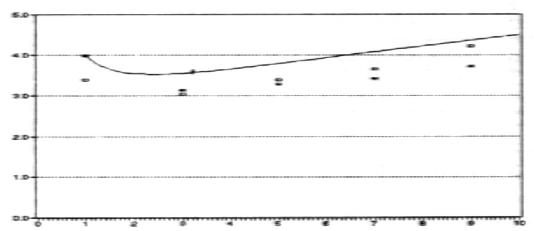

Fig. 8 exhibits the normalized transit time of the composite transistor in terms of the number of transistors connected to the drain side. The transit time increases very slowly with the increasing number of parallel-connected transistors at the drain side.

# IV. DISCUSSION AND CONCLUSIONS

All the experimental results presented in this paper were obtained from samples of the C4007 integrated circuit. However, we have also measured DC characteristics of MOS composite transistors, made up of minimum channel-length (1.2um) unit transistors, integrated in the 7th CMOS Brazilian multiproject chip. The DC measurements in the integrated composite transistor have also corroborated the theoretical prediction stated in section II.

We have proposed in this paper a method to design composite transistors wider at the drain end than at the source end. These transistors can be designed to have a  $g_m/g_{ds}$  ratio substantially larger than that of a single transistor without the corresponding reduction in the cutoff frequency which would occur in a rectangular transistor. Hence, composite transistors are very useful for the design of simple scheme analog sections for high speed and low voltage applications.

The use of composite transistors is not limited to applications in gate arrays. They can also be employed in full custom circuits providing easy-to-implement equivalents to nonrectangular transistors [6]. Moreover, the IC designer can benefit from better matching properties if unit transistors in composite devices are placed so that the effect of parameter gradients is minimized.

- S. MASUDA et al: "A CMOS analog and digital masterslice LSI", in ISSCC Dig. Tech. Papers, 1987, pp. 146-147.

- [2] P. DUCHENE, M. J. DECLERCQ: "A highly flexible sea-of-gates structure for digital and analog applications", IEEE JSSC, vol. 24, no. 3, June 1989, pp. 576-584.

- [3] S. KAWADA et al: "1.5-um CMOS gate arrays with analog/digital macros designed using common base arrays: , IEEE JSSC, vol. 24, no. 4, August 1989, pp. 985-990.

- [4] Y. P. TSIVIDIS. "Operation and modeling of the MOS transistor", Mc-Graw Hill, New York, 1987.

- [5] C. ENZ: "High precision CMOS micropower amplifier", Ph. D. Thesis no. 802, EPFL, Switzerland, 1989.

- [6] B. RICCO: "Effect of channel geometries on FET output conductance in saturation", IEEE ED Lett, vol. EDL-5, no. 9, September 1984, pp. 353-356.

Fig. 1 - Composite transistors

(a) Trapezoidal transistor (T-transistor)

(b) Rectangular transistor (R-transistor)

Fig. 2 - Series connected transistors

Fig. 3 - DC characteristics of a unit transistor and a square  $(3 \times 3)$  composite transistor.

Fig. 4 - Voltages at internal node X of the composite transistors of Fig. 1.

Fig. 5 - (a) DC characteristics of the composite transistors of Fig. 1. (b) Detail of the saturation region.

Fig. 6 - Circuit for the measurement of gate-to-source capacitance.

Fig. 7. Experimental results for the gate-to-source coupling in the R and T-transistors (Vdb=Vgb= -3V, Vsb= 0V)

Fig. 8. Normalized transit time of the T-transistor (m is the number of parallelconnected transistors at the drain side)

theoretical;

□ measured at Vgs= -2V;

\* measured at Vgs= -3V;