- 1 COLINGE, J.P.: 'Silicon-on insulator technology: Materials to VLSI' (Kluwer Academic Publishers, 1991)

- 2 GAO, M., COLINGE, J.P., LAUWERS, L., WU, S., and CLAES, C.: 'Twin MOSFET structure for suppression of kink and parasitic bipolar effects in SOI MOSFETs at room and liquid helium temperatures', Solid-State Electron., 1992, 35, (4), pp. 505-512

- 3 SIMOEN, E., and CLAES, C.: Impact of twin-gate concept on silicon-on-insulator inverters', Electron. Lett., 1994, 30, pp. 454-456

- 4 CHOI, J.Y., and FOSSUM, J.G.: 'Analysis and control of floating-body bipolar effects in fully depleted SOI MOSFETs', *IEEE Trans.*, 1991, ED-38, pp. 1384–1391

- 5 BUNYAN, R.J.T., UREN, M.J., THOMAS, N.J., and DAVIS, J.R.: 'Degradation in thin-film SOI MOSFETs caused by single-transistor latch', IEEE Electron Device Lett., 1990, 11, pp. 359–361

## MOSFET threshold extraction from voltageonly measurements

C. Galup-Montoro, M.C. Schneider, A.L. Koerich and R.L.O. Pinto

Indexing terms: MOSFET, Semiconductor device characterisation

The authors describe a method for determining the MOS transistor parameters from voltage measurements by considering two transistors in series. The voltage characteristics at the intermediate node of the two connected transistors allow easy and direct determination of the threshold voltage, the pinch-off voltage and the slope factor.

Introduction: The accurate determination of MOSFET parameters is important for IC process development, manufacturing and design. In recent years, methods based on the analysis of the drain current for the extraction of MOSFET parameters have been proposed [1,2]. The main drawback of these methods is that a single measured variable, the drain current, is employed to determine two independent physical variables, the threshold voltage, related to the carrier charge density, and the mobility. In the classical determination of the charge density and the mobility using the Hall effect both the current and the Hall voltage have to be measured [3].

This Letter presents a new method for the extraction of MOS-FET parameters based on the properties of the series connection of MOS transistors [4]. The voltage at the intermediate node of the connected transistors provides the information needed to determine the parameters related to the chanel charge, namely, the zero bias threshold voltage  $(V_{T0})$ , the pinch-off voltage  $(V_P)$  and the slope factor (n).

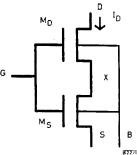

Fig. 1 Series association of transistors

Principle of method: We consider here the series connection of transistors, as shown in Fig. 1, i.e. the gate and bulk terminals are common to both transistors. The series connection can be viewed as a single transistor [4], where the potential at an internal point of the channel is accessible. To determine the theoretical potential at

the intermediate node, we consider a first order transistor model as follows. In the triode region and in strong inversion, the drain current of an MOS transistor can be written [5-7] as

$$I_D = \frac{W}{L} \mu_{eff} C'_{ox} \frac{n}{2} \left[ (V_P - V_S)^2 - (V_P - V_D)^2 \right] \qquad (1)$$

where all voltages are referred to the substrate.  $\mu_{gf}$  is the effective

where all voltages are referred to the substrate.  $\mu_{eff}$  is the effective mobility, which in the usual approximations for long-channel devices depends only on the gate voltage [1,6]. The pinch-off voltage [5-7] is given by

$$V_P \simeq \frac{V_G - V_{T0}}{n} \tag{2}$$

The undefined symbols in eqns. 1 and 2 have their usual meanings [5,6]. For the series connection of transistors (Fig. 1), assuming that the drain currents of  $M_S$  and  $M_D$  are equal and that the two transistors have the same width and length, we obtain

$$(V_P - V_X)^2 = \frac{1}{2}(V_P - V_D)^2 + \frac{1}{2}(V_P - V_S)^2$$

(3)

from the application of eqn. 1 for both transistors. On the verge of saturation of the transistor  $M_D$ ,  $V_D = V_P$ ; therefore, eqn. 3 reduces to

$$V_X \simeq \frac{V_G - V_{T0}}{n} \left( 1 - \frac{1}{\sqrt{2}} \right) + \frac{V_S}{\sqrt{2}}$$

(4)

In this work we have used eqn. 4 to determine  $V_{70}$ ,  $V_{P}$  and n.

Results and discussion: To test the above method of parameter extraction, measurements for the series connection (Fig. 1) of two identical ( $W = 6 \mu m$ ,  $L = 5 \mu m$ ) N-channel transistors from a  $2 \mu m$  CMOS technology have been performed.

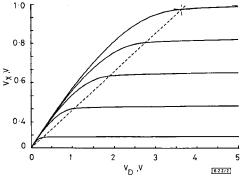

Fig. 2 Experimental intermediate node voltage  $V_X(V_D)$  characteristics for  $V_G=1,\,2,\,3,\,4$  and  $5\,V$  and  $V_S=0$

Fig. 2 plots the measured voltage  $V_X$  at the intermediate node in the series connection of transistors as a function of  $V_D$ . The dashed line  $V_X = (1 - 1/\sqrt{2})V_D$  is the theoretical boundary between the triode and the saturation regions, according to eqn. 4.

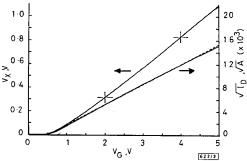

Fig. 3 Experimental intermediate node voltage  $V_{\lambda}(V_G)$  and square root of drain current  $\sqrt{I_D(V_G)}$  for  $V_D=V_G$  and  $V_S=0$

Fig. 3 displays the measured  $\sqrt{I_D(V_G)}$  and  $V_X(V_G)$  characteristics for the series connection of the transistors. The zero bias threshold voltages obtained from the linear extrapolation of the  $\sqrt{I_D(V_G)}$  and

$V_X(V_G)$  curves to the X-axis are 499 and 762 mV, respectively. The determination of  $V_{70}$  from the  $V_{X}(V_{G})$  curve is direct because this plot is linear for values of  $V_G$  larger than, say, 2V. The determination of  $V_{T0}$  from the  $\sqrt{I_D(V_G)}$  curve, however, is not precise because of the mobility dependence on the transversal field, which depends on  $V_G$ . It should be noted here that the extraction of the threshold voltage from the  $V_X(V_G)$  curve does not depend on the value of the effective carrier mobility. The slope factor n is easily determined from the gradient of the  $V_{\chi}(V_G)$  curve, which is equal to  $(1 - 1/\sqrt{2})/\sqrt{2}$ n, according to eqn. 4. In our case, the gradient is 0.256; hence, n

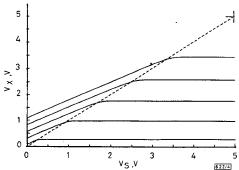

Fig. 4 shows  $V_X(V_S)$  curves. The slope of the curves for low values of  $V_s$ , i.e. for strong inversion operation, is ~1/ $\sqrt{2}$ , according to eqn. 4. The value of the pinch-off voltage for any value of  $V_G$  is determined by the intersection of the tangent to the curve  $V_x(V_s)$ for low  $V_s$  and the straight line  $V_x = V_s$ , according to eqn. 4.

Fig. 4 Experimental intermediate node voltage  $V_X(VS)$  characteristics for  $V_G = 1$ , 2, 3, 4, and 5 V with  $V_D = V_G$

Conclusion: We have proposed a direct method to determine the MOS transistor parameters that are related to the channel charge without using current measurements. We have used information provided by the voltage at the intermediate node of the series connection of transistors in order to determine the zero bias threshold voltage, the pinch-off voltage and the slope factor. The voltage measurements presented in this work together with the drain current measurement can be used to precisely determine the effective mobility dependence on the gate voltage.

Acknowledgments: The authors are greatly indebted to F. Krummenacher from EPF - Lausanne, Switzerland, for introducing them to the EPFL MOSFET model and to MICRODUL for supplying the test devices.

© IEE 1994

21 June 1994

Electronics Letters Online No: 19940979

Galup-Montoro, M.C. Schneider, A.L. Koerich and R.L.O. Pinto INSE-EEL, Universidade Federal de Santa Catarina, CP 476, 88 040 900, Florianopolis SC, Brazil)

## References

- GHIBAUDO, G.: 'New method for the extraction of MOSFET parameters', Electron. Lett., 1988, 24, (9), pp. 543-545

- CORSI, F., MARZOCCA, C., and PORTACCI, G.V.: 'New experimental technique for fast and accurate MOSFET threshold extraction', Electron. Lett., 1993, 29, (15), pp. 1358-1360

- MILLMAN, J., and HALKIAS, C.C.: 'Integrated electronics: Analog and digital circuits' (McGraw-Hill, New York, 1972)

- GALUP-MONTORO, C., SCHNEIDER, M.C., and LOSS, I.J.B.: 'Low output conductance composite Mossets for high frequency analog design'. Proc. 1994 IEEE Int. Symp. on Circuits and Systems, London, UK, May 1994, Vol. 5, pp. 783-786

- VITTOZ, E.: 'MOS transistor'. Intensive Summer Course on CMOS VLSI Design, Analog&Digital, Lausanne (EFPL), Switzerland

- ENZ, C.C.: 'High precision CMOS micropower amplifiers'. PhD Thesis No. 802, EPF-Lausanne, Switzerland, 1989

- GODFREY, M.D.: 'CMOS device modeling for subthreshold circuits', IEEE Trans., 1992, CAS-39, (8), pp. 532-539 (part II)

## **ESTIMATION OF LENGTH FOR ELECTRONICS LETTERS**

**VERSION 4.0**

Title

Text

1 column cm per 80 characters

Indexing terms 1.5 column cm (this includes adjacent space)

Abstract 1 column cm per 165 characters

Authors 1 column cm, plus 1 column cm for each address

> 1 column cm per 165 characters (it is easiest to estimate the number of characters, including spaces, per line and the number of lines per page); add 0.5 or even 1 column cm for each equation or line in a matrix unless it is well displayed; counts of words or even characters made by word processors

are not reliable for this purpose

References 1 column cm each

1 to 2 column cm for the title, 0.4 column cm for each line, including blanks; Tables

wide tables will be reshaped by editorial staff and the estimate adjusted accordingly

Figure captions 1 column cm for the main caption, 0.33 column cm per line for subcaptions,

including keys which would be moved from the graphics

**Figures** These are usually reduced to single column width (8.6 cm) at constant ratio of height to width;

if the Figure is illegible at this reduction, the editing staff will redraw it and the height will be

recalculated accordingly