# Explicit formula for harmonic distortion in SC filters with weakly nonlinear capacitors

M.C. Schneider C. Galup-Montoro J.C.M. Bermudez

Indexing terms: Switched capacitor filters, Nonlinear capacitors, Capacitor distortion, VLSI

Abstract: An explicit formula is derived for harmonic distortion as a function of the capacitance nonlinearities and of the transfer function of the same filter implemented with linear capacitors. Application of the proposed formula to SC filters with capacitors implemented by MOSFET gates shows that harmonic distortions as low as -40 to -60 dB can be obtained.

#### 1 Introduction

Switched capacitor filters have been extensively employed in practical analogue integrated circuit implementations for the past decade [1]. Presently, several complex mixed-mode circuits have their analogue parts implemented using switched capacitor circuits [2-5]. Nevertheless, the use of linear analogue circuits in systems that are predominantly digital imposes special challenges owing to the nonlinear nature of the capacitors available in VLSI.

Usually, the nonlinear problems have been overcome by utilising nonstandard MOS processes, the most typical solution being the inclusion of a second polysilicon layer (double-poly processes). Though this solution has enabled the design of linear switched capacitor filters with performances rarely matched by other types of integrated analogue circuit implementations, the corresponding cost increase still remains a drawback to be eliminated or, at least, minimised.

A good measure of the impact of this drawback is the recent appearance of new analogue systems design techniques compatible with standard digital prcesses. One such technique is the switched current (SI) approach [6, 7]. Obviously, the shift towards a new type of circuit is always accompanied by new design issues. For example, SI filters require a linear voltage-to-current converter at their input

Recently, a new approach has been proposed [8] for the design of SC filters integrated in standard digital processes. The filter is designed using traditional SC design techniques and the capacitors are implemented by the nonlinear MOS gate structure biased in the accumulation region. Nevertheless, a proper evaluation of this possibility depends on the determination of the output harmonic distortion of an SC filter.

Circuits with weak nonlinearities can be analysed using Volterra series techniques [9, 10]. Such methods, however precise, usually generate quite complex mathematical expressions and therefore must be implemented in numerical [11] or symbolic simulators [12]. Hence, closed-form expressions for distortion would serve as important guidelines for circuit designers. This paper uses the method of small perturbations [13] to determine explicit expressions for harmonic distortion in SC filters owing to the use of weakly nonlinear capacitors.

#### 2 Transistor-only switched capacitor filters

The use of the MOS structure in accumulation or strong inversion to realise onchip capacitors [8] requires a suitable circuit arrangement to provide the necessary plate bias. The required bias can be accomplished by biasing either all the bottom plates or all the top plates to a DC reference voltage, say  $V_R$ .

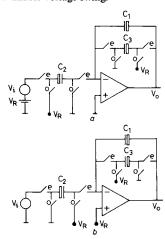

Fig. 1 shows two possible biasing arrangements for a lossy integrator circuit. In Fig. 1a the proper biasing is provided to the capacitor plates connected to voltage sources [8]. Analysis of this circuit shows that

$$V_o^e(z) = -\frac{C_2}{(C_1 + C_3) - C_1 z^{-1}} V_i^e(z)$$

$$-\frac{C_2}{(C_1 + C_3) - C_1 z^{-1}} V_r^e(z)$$

$$+\frac{(C_2 + C_3) z^{-1/2}}{(C_1 + C_3) - C_1 z^{-1}} V_r^o(z)$$

(1)

where the variables V(z) are the z-transforms of the signals sampled at the even or odd clock phases. For a constant reference voltage  $V_R$ ,  $V_i^e(z) = V_R/(1-z^{-1})$  and  $V_i^e(z) = V_R z^{-1/2}/(1-z^{-1})$ . Then, for  $v_i = 0$  and z = 1 (DC),  $V_i^e(1) = V_R$ . This clearly guarantees the proper biasing for  $C_1$  and  $C_3$ .

In the arrangement of Fig. 1b the operational amplifier must admit a common-mode input voltage equal to  $V_R$ .

The authors acknowledge the support of the CNPq Brazilian Council for Science and Technology.

<sup>©</sup> IEE, 1994

Paper 1447G (E10), first received 5th August 1993 and in revised form 21st June 1994

The authors are with the Laboratorio de Instrumentacao Eletronica LINSE, Departamento de Engenharia Eletrica, Universidade Federal de Santa Catarina, CP476 - 88.040.900 Florianopolis SC Brazil

On the other hand, the same reasoning shows that the DC steady-state output voltage  $V_o$  is equal to zero, maximising the available voltage swing.

Fig. 1 Two bias schemes for lossy SC integrator

- a Source bias

- b Amplifier bias

#### 3 Analysis of SC filters implemented with nonlinear capacitors

The main sources of harmonic distortion in SC filters are the capacitor nonlinearity, the op-amp gain nonlinearity and finite slew-rate, and the charge injection by the switches [11, 13]. The objective of this work is to evaluate the possibility of SC filter implementations using nonlinear capacitors. Thus, the following analysis considers SC networks implemented with ideal op-amps and switches. It is also assumed that the same function f[v] can be used to model the nonlinearities of all capacitors in the network [13, 14]. This condition can be accurately fulfilled in an integrated circuit. Hence, the charge stored at time t = nT in a capacitor  $C_A$  with a voltage v(nT) across its terminals is

$$q_A = C_A v(nT) = C_{A0} f[v(nT)]v(nT)$$

(2)

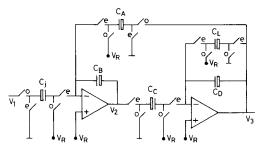

where  $C_{A0}$  is the capacitance value for a signal voltage equal to zero. To avoid cumbersome notations, the following development is presented for a second-order SC network. In the network shown in Fig. 2, the capacitor plates have been biased using the scheme presented in Fig. 1b. Writing the charge conservation equations around the DC operating point and expressing the capacitance charges as in eqn. 2 yields, at t = nT (even phase),

$$-C_{J0} f[v_{1}(nT - T/2)]v_{1}(nT - T/2)$$

$$-C_{A0} f[v_{3}(nT - T)]v_{3}(nT - T)$$

$$= -C_{B0} f[v_{2}(nT)]v_{2}(nT)$$

$$+ C_{B0} f[v_{2}(nT - T)]v_{2}(nT - T)$$

$$C_{C0} f[v_{2}(nT)]v_{2}(nT) + C_{L0} f[v_{3}(nT)]v_{3}(nT)$$

$$= -C_{D0} f[v_{3}(nT)]v_{3}(nT)$$

$$+ C_{D0} f[v_{3}(nT - T)]v_{3}(nT - T)$$

(3b)

In the general case, this is a system of nonlinear equations on the node voltages. However, performing the change of variable [14]

$$f[v_i(\cdot)]v_i(\cdot) = u_i(\cdot) \tag{4}$$

the system of eqn. 3 is transformed into a set of linear equations on the variables  $u_i(\cdot)$ , as follows:

$$-C_{J0} u_1(nT - T/2) - C_{A0} u_3(nT - T)$$

$$= -C_{B0} u_2(nT) + C_{B0} u_2(nT - T)$$

$$C_{C0} u_2(nT) + C_{L0} u_3(nT)$$

(5a)

(5b)

Applying the z-transform to both equations and solving for the transform  $U_3^e(z)$  of the output variable yields the transfer function

$= -C_{D0} u_3(nT) + C_{D0} u_3(nT - T)$

$$H_{u}(z) = \frac{U_{1}^{e}(z)}{U_{1}^{0}(z)}$$

$$= \frac{-C_{J0} C_{C0} z^{-1/2}}{C_{B0}(C_{L0} + C_{D0}) + (C_{A0} C_{C0})} (6)$$

$$-2C_{B0} C_{D0} - C_{B0} C_{L0})z^{-1} + C_{B0} C_{D0} z^{-2}$$

This expression is exactly the same as the transfer function  $H(z) = V_0^{\epsilon}(z)/V_0^{1}(z)$  of the same network implemented with linear capacitors.

These results can be extended to all SC networks satisfying the following conditions [14]:

Condition 1: after the settling time corresponding to each clock phase, the voltage across any capacitor must depend only on a single node voltage.

Condition 2: all capacitors connected to the same op-amp output must present identical nonlinearities expressed by the function  $f(v_x)$ ,  $v_x$  the voltage at the op-amp output node.

Hence, for an Nth-order filter, eqn. 6 assumes, aside from a possible half-period delay, the general form

$$H_{u}(z) = \frac{U_{out}(z)}{U_{in}(z)} = \frac{\sum_{i=1}^{N} n_{i} z^{-i}}{\sum_{i=1}^{N} d_{i} z^{-i}}$$

(7)

# 4 Harmonic distortion due to capacitor nonlinearities

Now determine the output harmonic distortion for the practical case of networks implemented with weakly non-linear capacitors. To this end, study the time-domain behaviour of SC networks satisfying the aforementioned topological constraints. According to eqns. 4 and 7, the voltage nonlinear difference equation describing an SC network is

$$\sum_{i=1}^{N} d_{i} f[v_{out}(nT - iT)] v_{out}(nT - iT)$$

$$= \sum_{i=1}^{N} n_{i} f[v_{in}(nT - iT)] v_{in}(nT - iT)$$

(8)

To determine the output voltage harmonic distortion, eqn. 8 must be solved for an input signal  $v_{in}(nT) = V_m \cos(\omega_0 nT)$ . Considering weak nonlinearities, the following simplifying assumptions can be made [13]:

(i) The nonlinear function f[v] can be described by a Taylor series, i.e.

$$f[v] = 1 + \sum_{i=1}^{\infty} \alpha_i v^i \tag{9}$$

(ii) The terms of the series expansion responsible for the nonlinearities satisfy

$$\sum_{l=1}^{\infty} |\alpha_l v^l| \leqslant 1 \tag{10}$$

IEE Proc.-Circuits Devices Syst., Vol. 141, No. 6, December 1994

for both the input and output voltages. Under this assumption, the fundamental frequency component at the output  $V_1 \cos(\omega_0 nT + \phi_1)$  can be approximated by the output of the ideal linear circuit. Hence

$$V_1 \simeq V_m |H(e^{j\omega_0 T})| \quad \phi_1 \simeq \text{ phase of } H(e^{j\omega_0 T})$$

(11)

(iii) The nonlinear terms  $\alpha_l[v_{out}(nT-iT)]^{l+1}$  in eqn. 8 can be approximated by substituting  $v_{out}$  for the ideal linear circuit output voltage:

$$\alpha_l V_1^{l+1} [\cos(n\omega_0 T - i\omega_0 T + \phi_1)]^{l+1}$$

(12)

Substituting eqns. 9, 11 and 12 into eqn. 8 leads, after some algebraic manipulations (Appendix 8.1), to the expression for the output distortion owing to the usually dominant [11, 13, 15] 2nd harmonic:

$$HD_{2} = \frac{V_{2}}{V_{1}} = \left| a_{2}(V_{m}) \frac{H(e^{2j\omega_{0}T})}{|H(e^{j\omega_{0}T})|} - a_{2}(V_{1}) \frac{H^{2}(e^{j\omega_{0}T})}{|H(e^{j\omega_{0}T})|^{2}} \right|$$

(1)

where  $a_2(V)$  is a nonlinear function defined (Appendix 8.2) by

$$a_2(V) = \frac{\alpha_1 V}{2} \binom{2}{0} + \frac{\alpha_3 V^3}{2^3} \binom{4}{1} + \frac{\alpha_5 V^5}{2^5} \binom{6}{2} + \cdots$$

(14)

#### 5 Experimental verification

The second-order lowpass SC network of Fig. 2 has been implemented as a discrete prototype. As nonlinear capa-

Fig. 2 Prototype SC biquad

citors, the capacitances from gate to short-circuited source and drain terminals of well-matched Motorola P5N40 power transistors have been used. A reference voltage  $V_R = -4 \, \mathrm{V}$  has been employed to obtain a voltage capacitance coefficient similar to that of an integrated gate capacitor, inside an n-well and biased in accumulation with  $V_{GS} = 2.5 \, \mathrm{V}$  [15].  $\mu \mathrm{A741}$  amplifiers and CD4066 analogue switches have been used.

To determine the distortion at the inverting  $(V_3)$  and noninverting  $(V_2)$  output nodes, the transfer functions have been evaluated using the nominal capacitance values, yielding

$$H_{inv}(z) = \frac{-0.08333}{1.33333 - 2.25z^{-1} + z^{-2}} z^{-1/2}$$

(15)

$$H_{ninv}(z) = \frac{0.33333 - 0.25z^{-1}}{1.33333 - 2.25z^{-1} + z^{-2}} z^{-1/2}$$

(16)

The magnitudes and phases of the corresponding frequency responses are shown in Fig. 3. In the experiments,

IEE Proc.-Circuits Devices Syst., Vol. 141, No. 6, December 1994

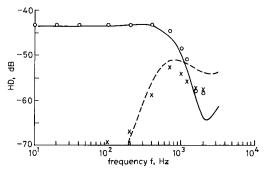

only the second harmonic has been detectable (above -80 dB). Hence, the theoretical results have been determined from eqn. 13, with  $a_2(V) \simeq 1/2\alpha_1 V$ ,  $\alpha_1 = 0.0045 V^{-1}$ , determined as in Reference 15. In this case, eqn. 13 reduces to the simple form:

$$HD_2 \simeq \alpha_1 V_m \left| \frac{H(e^{2j\omega_0 T}) - H^2(e^{j\omega_0 T})}{2H(e^{j\omega_0 T})} \right| \tag{17}$$

Fig. 4 presents both the theoretical and experimental harmonic distortions at the inverting and noninverting outputs. The same prototype has also been built with

Fig. 3 Theoretical responses of example filter of Fig. 2

a Magnitude response  $\cdots$  noninverting output  $V_2$  inverting output  $V_3$  b Phase response  $\cdots$  noninverting output  $V_2$  inverting output  $V_2$

Fig. 4 Second-order harmonic distortion of example filter of Fig. 2 as function of input frequency

$\frac{V_{R} = -4 \text{ V; } V_{in} = 3V_{pkpk}; T^{-1} = 20 \text{ kHz}}{\text{theoretical at inverting output } V_{3}}$

$\bigcirc\bigcirc\bigcirc$  experimental theoretical at noninverting output  $V_2$

$\times \times \times$  experimental

linear capacitors. The distortion measured in this case was at least 20 dB below the distortions in Fig. 4. This indicates that the effects depicted in Fig. 4 have indeed been caused mainly by the capacitance nonlinearities and not by the switches or operational amplifiers. An interesting point to be observed is that the noninverting output presents a distortion substantially smaller than the inverting one. This is explained by the fact that, for the noninverting output,  $H(e^{j2\omega_0T}) \simeq H(e^{j\omega_0T}) \simeq 1$  for  $\omega_0$ close to zero and therefore from eqn. 17,  $HD_2 \simeq 0$ .

#### Conclusions

An explicit formula for the harmonic distortion due to weak nonlinearities of the capacitors in SC filters has been presented. It has been shown that the harmonic distortion is predictable from the knowledge of the capacitance nonlinearities and from the transfer function of the same filter implemented with linear capacitors. Unlike numerical methods, this formula provides direct information about harmonics as a function of the frequency.

### References

- 1 GRAY, P.R., WOOLEY, B.A., and BRODERSEN, R.W. (Eds.): Analog MOS Integrated Circuits II' (IEEE Press, 1988, New York,

- 2 SHIH, C.-C., LAM, K.-K., LEE, K.-L., and SCHALK, R.W.: 'A CMOS 5-V analog front end for 9600-bit/s facsimile modem', IEEE

- J. Solid-State Circuits, 1987, SC-22, (6), pp. 990-995 YEUNG, M.K., CHEUNG, P.S., and ARULANANTHAN, R.: 'A 5-V front-end chip for a universal voice-band modem', IEEE J.

- Solid-State Circuits, 1990, SC-25, (6), pp. 1440-1449 4 HASPESLAGH, J.J., SALLAERTS, D., REUSENS, P.P., VAN-WELSENAERS, A., GRANEK, R., and RABAEY, D.: 'A 270-Kb/s 35-mW modulator IC for GSM cellular radio hand-held terminals',

- IEEE J. Solid-State Circuits, 1990, SC-25, (6), pp. 1450-1457

5 CASTELLO, R., TOMASINI, L., PERNICI, S., SALERMO, F., MAZZUCO, M., and FERRY, M.: 'Analog front end for an ECBM transceiver for ISDN', IEEE J. Solid-State Circuits, 1990, SC-25, (6),

- 6 HUGHES, J.B., BIRD, N.C., and MACBETH, I.C.: 'Switchedcurrents-a new technique for analog sampled-data signal processing. Proceedings of IEEE international symposium on Circuits and systems, Portland, USA, May 1989, pp. 1584-1587

HUGHES, J.B., MACBETH, I.C., and PATTULLO, D.M.: Switched-current filters, IEE Proc. G, 1990, 137, (2), pp. 156-162

MONTORO, C.G., and BERMUDEZ, J.C.M.: Switched capacitor

- circuits fully compatible with digital Si-gate single poly technology'. Proceedings of 31st midwest symposium on Circuits and Systems, St. Louis, USA, Aug. 1988, pp. 1-3

9 BEDROSIAN, E., and RICE, S.O.: 'The output properties of Vol-

- terra systems (nonlinear systems with memory) driven by harmonic and Gaussian inputs', Proc. IEEE, 1971, 59, (12), pp. 1688-1707 10 BUSSGANG, J.J., EHRMAN, L., and GRAHAM, J.W.: 'Analysis

- of nonlinear systems with multiple inputs', Proc. IEEE, 1974, 62, (8),

- 11 VANDEWALLE, J., RABAEY, J., VERCRUYSSE, W., and DE MAN, H.J.: 'Computer-aided distortion analysis of switched capacitor filters in the frequency domain', IEEE J. Solid-State Circuits, 1983, SC-18, (3), pp. 324-333 WAMBACO, P., GIELEN, G., and SANSEN, W.: 'Symbolic simu-

- lation of harmonic distortion in analog integrated circuits with weak nonlinearities'. Proceedings of IEEE international symposium on

- Circuits and Systems, New Orleans, USA, May 1990, pp. 536-539

13 LEE, K.L., and MEYER, R.G.: 'Low-distortion switched capacitor filter design techniques', *IEEE J. Solid-State Circuits*, 1985, SC-20, (6), pp. 1103-1113

- 14 BERMUDEZ, J.C.M., SCHNEIDER, M.C., and MONTORO, C.G.: Compatibility of switched-capacitor filters with VLSI processes', *IEE Proc.-G.*, 1992, 139, (4), pp. 413–418

- 15 BEHR, A.T., SCHNEIDER, M.C., NOCETI FILHO, S., and MONTORO, C.G.: 'Harmonic distortion caused by capacitors implemented with MOSFET gates', IEEE J. Solid-State Circuits, 1992 37 (10) 673 1873 1873 1874 1992, 27, (10), pp. 1470-1475

#### Appendix

## Derivation of harmonic distortion Substituting eqn. 9 into eqn. 8 and rearranging conve-

niently the terms yields

$$\sum_{i=1}^{N} d_{i} v_{out}(nT - iT)$$

$$= \sum_{i=1}^{N} n_{i} v_{in}(nT - iT) + \sum_{i=1}^{N} n_{i} \sum_{l=1}^{\infty} \alpha_{l} v_{in}^{l+1}(nT - iT)$$

$$- \sum_{i=1}^{N} d_{i} \sum_{l=1}^{\infty} \alpha_{l} v_{out}^{l+1}(nT - iT)$$

(18)

Ď

If assumption (iii) holds, and  $V_{in}(nT) = V_m \cos(\omega_0 nT)$ , eqn. 18 can be approximated by

$$\begin{split} \sum_{i=1}^{N} d_{i} v_{out}(nT - iT) \\ &\simeq \sum_{i=1}^{N} n_{i} V_{m} \cos (n\omega_{0} T - i\omega_{0} T) + \sum_{i=1}^{N} n_{i} V_{m} \sum_{l=1}^{\infty} \alpha_{l} V_{m}^{l} \\ &\times \left[\cos (n\omega_{0} T - i\omega_{0} T)\right]^{l+1} - \sum_{i=1}^{N} d_{i} V_{1} \sum_{l=1}^{\infty} \alpha_{l} V_{1}^{l} \\ &\times \left[\cos (n\omega_{0} T - i\omega_{0} T + \phi_{1})\right]^{l+1} \end{split} \tag{19}$$

where  $V_1 \simeq V_m |H(e^{j\omega_0 T})|$  and  $\phi_1 \simeq$  phase of  $H(e^{j\omega_0 T})$ . Substituting the sums of the powers of the cosine functions in eqn. 19 by their Fourier expansions (Appendix 8.2) and rearranging the terms yields

$$\sum_{i=1}^{N} d_{i} v_{out}(nT - iT)$$

$$\simeq V_{m} a_{0}(V_{m}) \sum_{i=1}^{N} n_{i} + V_{m} \sum_{i=1}^{N} n_{i} \cos (n\omega_{0} T - i\omega_{0} T)$$

$$+ V_{m} a_{1}(V_{m}) \sum_{i=1}^{N} n_{i} \cos (n\omega_{0} T - i\omega_{0} T)$$

$$+ V_{m} a_{2}(V_{m}) \sum_{i=1}^{N} n_{i} \cos (2n\omega_{0} T - 2i\omega_{0} T)$$

$$+ V_{m} a_{3}(V_{m}) \sum_{i=1}^{N} n_{i} \cos (3n\omega_{0} T - 3i\omega_{0} T) + \cdots$$

$$- V_{1} a_{0}(V_{1}) \sum_{i=1}^{N} d_{i} - V_{1} a_{1}(V_{1}) \sum_{i=1}^{N} d_{i}$$

$$\times \cos (n\omega_{0} T + \phi_{1} - i\omega_{0} T)$$

$$- V_{1} a_{2}(V_{1}) \sum_{i=1}^{N} d_{i} \cos (2n\omega_{0} T + 2\phi_{1} - 2i\omega_{0} T)$$

$$- V_{1} a_{3}(V_{1}) \sum_{i=1}^{N} d_{i} \cos (3n\omega_{0} T + 3\phi_{1} - 3i\omega_{0} T)$$

$$- \cdots \qquad (20)$$

Substituting the Fourier series expansion of  $v_{out}(nT)$  in

$$v_{out}(nT) = \sum_{k=0}^{\infty} V_k \cos(kn\omega_0 T + \phi_k)$$

(21)

into eqn. 20, the linear difference equation for the second harmonic is derived:

$$\begin{split} &V_{2} \sum_{i=1}^{N} d_{i} \cos \left(2n\omega_{0} T - 2i\omega_{0} T + \phi_{2}\right) \\ &= V_{m} a_{2}(V_{m}) \sum_{i=1}^{N} n_{i} \cos \left(2n\omega_{0} T - 2i\omega_{0} T\right) \\ &- V_{1} a_{2}(V_{1}) \sum_{i=1}^{N} d_{i} \cos \left(2n\omega_{0} T + 2\phi_{1} - 2i\omega_{0} T\right) \end{split} \tag{22}$$

IEE Proc.-Circuits Devices Syst., Vol. 141, No. 6, December 1994

Writing the cosine functions in exponential form and using the transfer function definition of the network with linear capacitors, yields:

$$\begin{split} V_2 \, e^{j\phi_2} &= \, V_m \, a_2(V_m) H(e^{j2\omega_0 T}) - V_1 a_2(V_1) e^{j2\phi_1} \\ &= \, V_1 \bigg\{ a_2(V_m) \, \frac{H(e^{j2\omega_0 T})}{|\, H(e^{j\omega_0 T})\,|} - a_2(V_1) \, \frac{H^2(e^{j\omega_0 T})}{|\, H(e^{j\omega_0 T})\,|^2} \bigg\} \end{split}$$

Provided that the hypotheses made in Sections 3 and 4 remain valid, an expression for the 3rd harmonic can be obtained following the same procedure, using the corresponding difference equation from eqn. 20. Hence,

$$HD_3 = \left| a_3(V_m) \frac{H(e^{j3\omega_0 T})}{|H(e^{j\omega_0 T})|} - a_3(V_1) \frac{H^3(e^{j\omega_0 T})}{|H(e^{j\omega_0 T})|^3} \right|$$

(24)

with  $a_3(V)$  given by eqn. 29 (Appendix 8.2)

8.2 Derivation of Fourier coefficients for expression eqn. 19

The Fourier Series expansion of

$$S = \sum_{i=1}^{\infty} \alpha_i V^i(\cos \theta)^{i+1}$$

(25)

can be obtained by writing  $(\cos \theta)^{l+1}$  as  $(e^{j\theta} + e^{-j\theta})^{l+1}/2^{l+1}$  and substituting it in eqn. 25 by its binomial expansion

$$(\cos \theta)^{l+1} = \frac{1}{2^{l+1}} \sum_{m=0}^{l+1} {l+1 \choose m} e^{i\theta(2m-l-1)}$$

(26)

leading to

$$S = \sum_{l=1}^{\infty} \frac{\alpha_l V^l}{2^{l+1}} \sum_{m=0}^{l+1} {l+1 \choose m} e^{j\theta(2m-l-1)}$$

(27)

Since S is an even and periodic function of  $\theta$ , it can be expressed as

$$S = \sum_{k=0}^{\infty} a_k(V) \cos(k\theta)$$

(28)

From eqn. 27, the magnitude of the second harmonic of S,  $a_2(V)$ , can be readily identified as the one presented in eqn. 14. In general, the magnitude of the kth harmonic of S can be written as

$$a_k(V) = \sum_{l=1}^{\infty} \frac{\alpha_{2l+k-3}}{2^{2l+k-3}} {2l+k-2 \choose l-1} V^{2l+k-3} \quad k \ge 2 \quad (29)$$